在當(dāng)今科技日新月異的時(shí)代,SoC(系統(tǒng)級(jí)芯片)已經(jīng)成為了各種電子設(shè)備的核心。而在這個(gè)復(fù)雜的系統(tǒng)中,時(shí)鐘芯片的作用尤為重要,它負(fù)責(zé)提供穩(wěn)定的時(shí)間基準(zhǔn),以確保整個(gè)系統(tǒng)的正常運(yùn)行。因此,研發(fā)一款高效、可靠且具有創(chuàng)新性的SOC時(shí)鐘芯片,成為了業(yè)界的重要課題。本文將從三個(gè)方面探討SOC時(shí)鐘芯片的研發(fā)理念:創(chuàng)新、高效和可靠性。

首先,創(chuàng)新是SOC時(shí)鐘芯片研發(fā)的靈魂。隨著科技的不斷進(jìn)步,人們對(duì)電子設(shè)備的性能要求越來(lái)越高,這就要求SOC時(shí)鐘芯片必須具備更高的集成度和更低的功耗。因此,創(chuàng)新是推動(dòng)SOC時(shí)鐘芯片技術(shù)發(fā)展的最重要的動(dòng)力。這包括采用新的工藝節(jié)點(diǎn)、開發(fā)新的架構(gòu)以及應(yīng)用新的算法等。只有不斷創(chuàng)新,才能使SOC時(shí)鐘芯片在性能和功耗上達(dá)到最優(yōu)的平衡,滿足市場(chǎng)的需求。

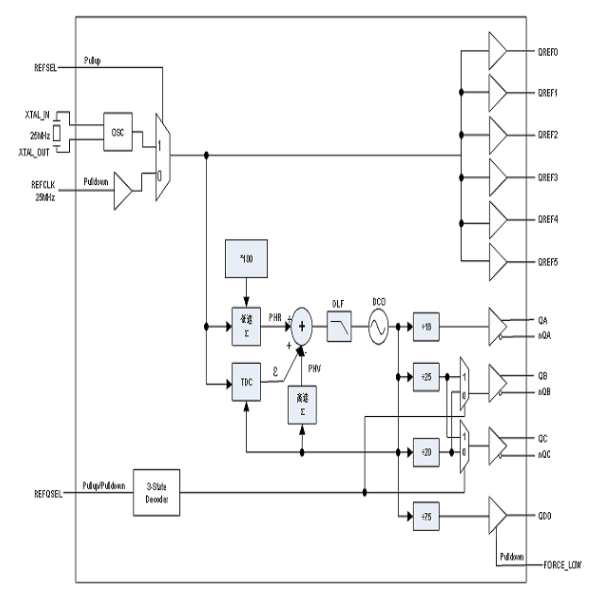

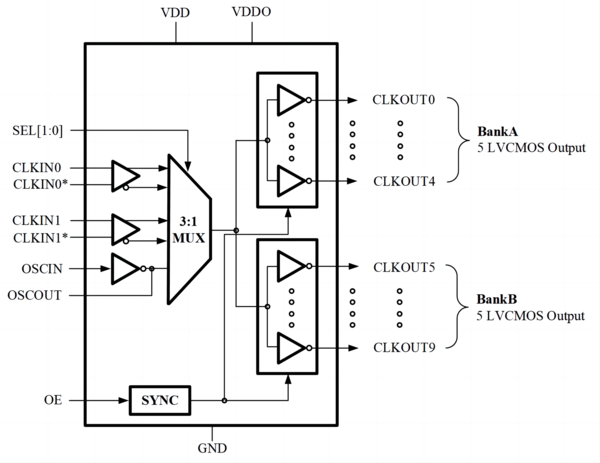

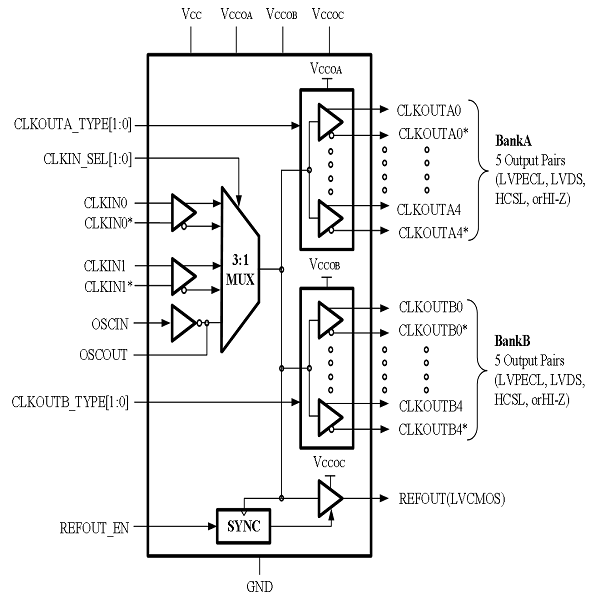

其次,高效是SOC時(shí)鐘芯片研發(fā)的目標(biāo)。高效的SOC時(shí)鐘芯片能夠有效地提高電子設(shè)備的運(yùn)行速度和穩(wěn)定性,從而提高用戶體驗(yàn)。為了實(shí)現(xiàn)這一目標(biāo),研發(fā)團(tuán)隊(duì)需要在設(shè)計(jì)和優(yōu)化過(guò)程中充分考慮時(shí)鐘管理的各個(gè)環(huán)節(jié),包括頻率合成、時(shí)鐘分配、噪聲抑制等。此外,還需要通過(guò)多核并行、異步復(fù)用等技術(shù)手段,進(jìn)一步提高SOC時(shí)鐘芯片的能效比。

最后,可靠性是SOC時(shí)鐘芯片研發(fā)的基礎(chǔ)。一個(gè)不穩(wěn)定的時(shí)鐘系統(tǒng)可能會(huì)導(dǎo)致電子設(shè)備的性能下降甚至損壞,給用戶帶來(lái)極大的不便。因此,SOC時(shí)鐘芯片必須具備高度的可靠性,能夠在各種環(huán)境條件下穩(wěn)定工作。為了實(shí)現(xiàn)這一目標(biāo),研發(fā)團(tuán)隊(duì)需要對(duì)SOC時(shí)鐘芯片進(jìn)行嚴(yán)格的測(cè)試和驗(yàn)證,確保其在各種工作條件下都能保持穩(wěn)定的性能。同時(shí),還需要采用冗余設(shè)計(jì)和故障自修復(fù)技術(shù),提高SOC時(shí)鐘芯片的抗干擾能力和自恢復(fù)能力。

總之,SOC時(shí)鐘芯片的研發(fā)理念是創(chuàng)新、高效和可靠性的完美結(jié)合。只有通過(guò)不斷的創(chuàng)新和優(yōu)化,才能設(shè)計(jì)出高性能、高效率和高可靠性的SOC時(shí)鐘芯片,滿足現(xiàn)代電子設(shè)備的發(fā)展需求。

時(shí)鐘系統(tǒng)

時(shí)鐘系統(tǒng)  芯片

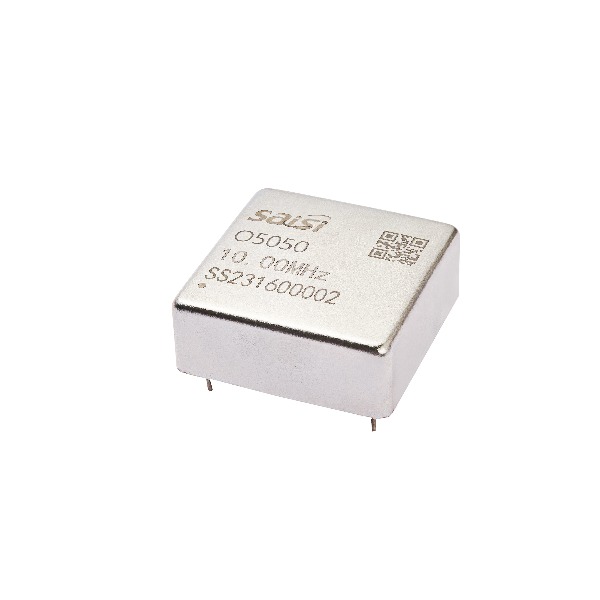

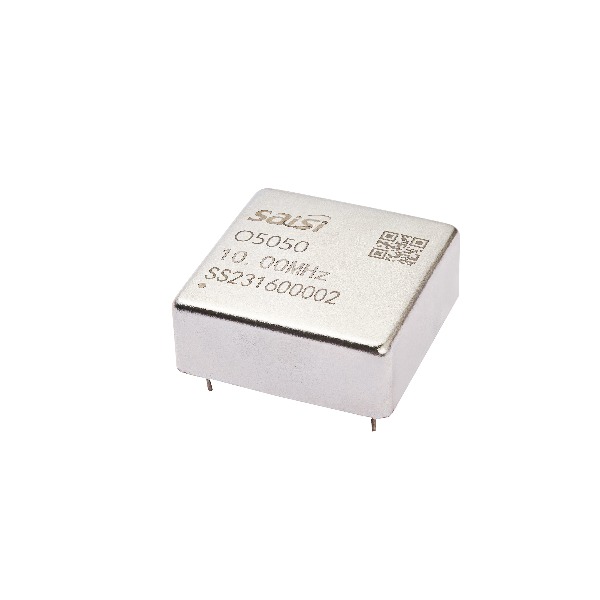

芯片  晶振&原子鐘

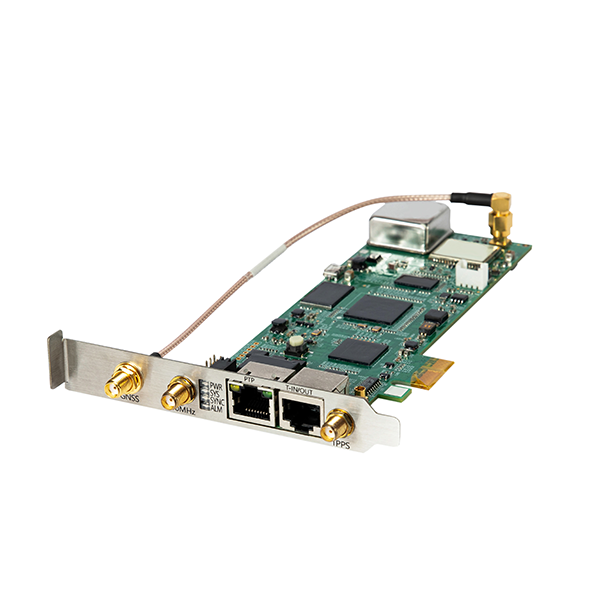

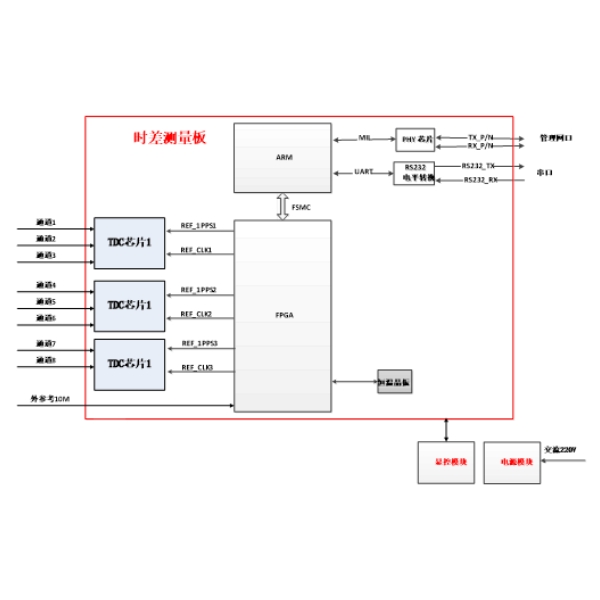

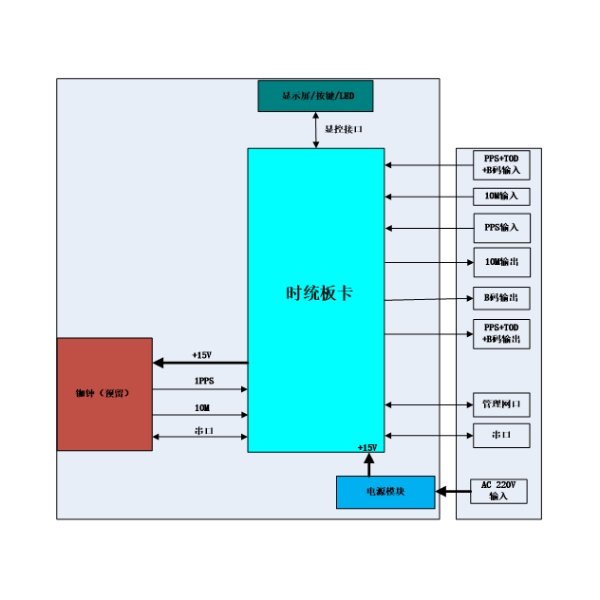

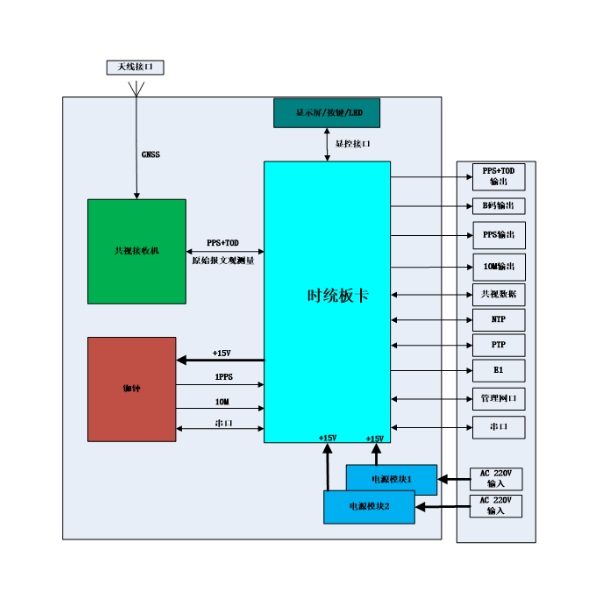

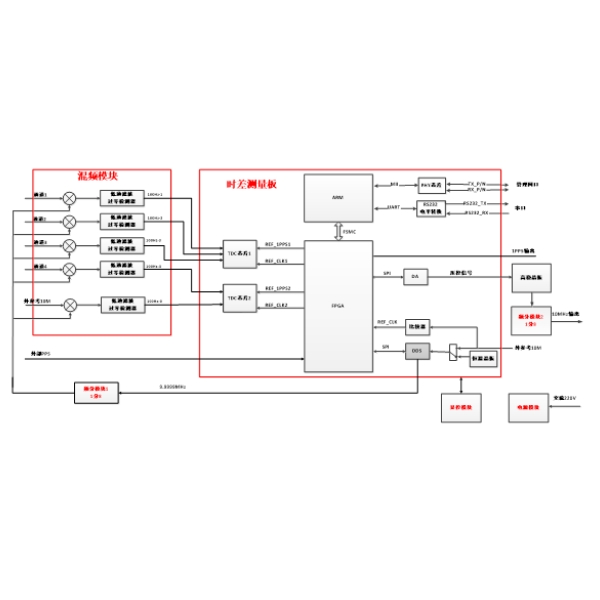

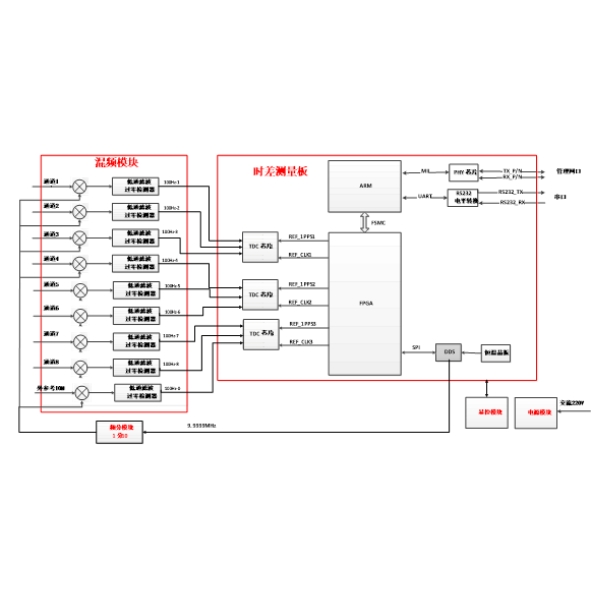

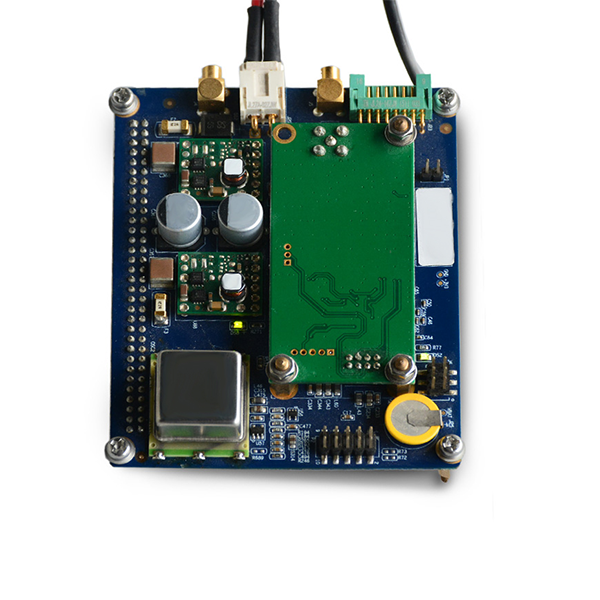

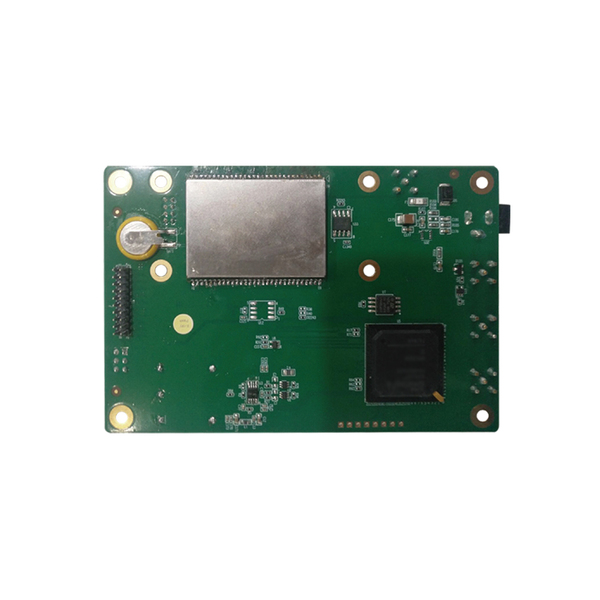

晶振&原子鐘  授時(shí)板卡 NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護(hù)裝置網(wǎng)同步設(shè)備/時(shí)頻一體化設(shè)備子母鐘系統(tǒng)BBU池時(shí)間同步時(shí)統(tǒng)設(shè)備鐘組設(shè)備測(cè)試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語(yǔ)音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片超低噪聲OCXO超高穩(wěn)OCXO小型化OCXO溫補(bǔ)晶振TCXO原子鐘時(shí)鐘模塊授時(shí)模塊

授時(shí)板卡 NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護(hù)裝置網(wǎng)同步設(shè)備/時(shí)頻一體化設(shè)備子母鐘系統(tǒng)BBU池時(shí)間同步時(shí)統(tǒng)設(shè)備鐘組設(shè)備測(cè)試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語(yǔ)音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片超低噪聲OCXO超高穩(wěn)OCXO小型化OCXO溫補(bǔ)晶振TCXO原子鐘時(shí)鐘模塊授時(shí)模塊 子母鐘系統(tǒng)TS8000

子母鐘系統(tǒng)TS8000 電力時(shí)間同步裝置TS3000(4U)

電力時(shí)間同步裝置TS3000(4U) NTP時(shí)間服務(wù)器TS3000(1U)

NTP時(shí)間服務(wù)器TS3000(1U) 時(shí)頻同步設(shè)備/網(wǎng)同步設(shè)備SM2000

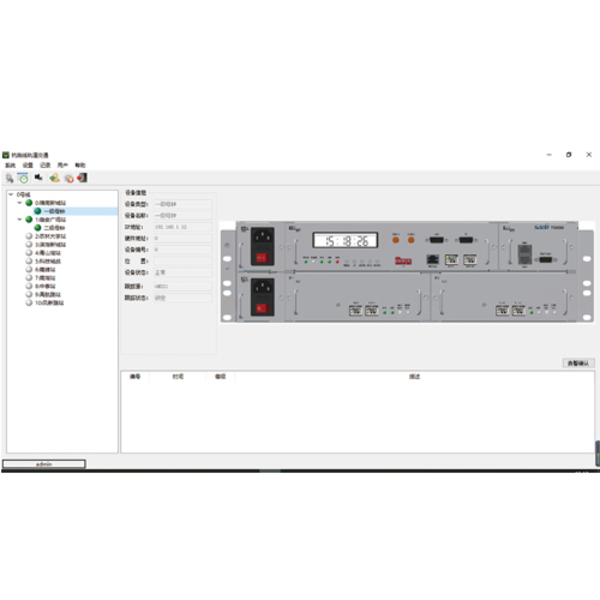

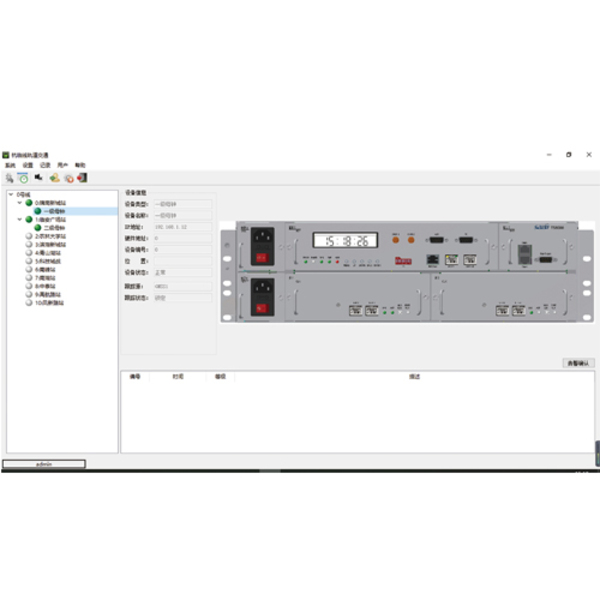

時(shí)頻同步設(shè)備/網(wǎng)同步設(shè)備SM2000 同步網(wǎng)綜合網(wǎng)管

同步網(wǎng)綜合網(wǎng)管 TS8000擴(kuò)展箱/NTP/RS422

TS8000擴(kuò)展箱/NTP/RS422 萬(wàn)兆接口NTP服務(wù)器NS7210

萬(wàn)兆接口NTP服務(wù)器NS7210 高性能NTP服務(wù)器NS7200

高性能NTP服務(wù)器NS7200 室外型PTP服務(wù)器LF7310

室外型PTP服務(wù)器LF7310 綜合時(shí)統(tǒng)設(shè)備LF7300

綜合時(shí)統(tǒng)設(shè)備LF7300 綜合時(shí)統(tǒng)設(shè)備LF7350

綜合時(shí)統(tǒng)設(shè)備LF7350 GPS/北斗智能分路系統(tǒng)GNSS100/200

GPS/北斗智能分路系統(tǒng)GNSS100/200

智能電網(wǎng)

智能電網(wǎng)

通信網(wǎng)絡(luò)

通信網(wǎng)絡(luò)

智慧交通

智慧交通

智能樓宇

智能樓宇

數(shù)據(jù)中心

數(shù)據(jù)中心

前沿領(lǐng)域

前沿領(lǐng)域

新聞資訊

新聞資訊

聯(lián)系我們

聯(lián)系我們

人才研學(xué)中心

人才研學(xué)中心

加入賽思

加入賽思

關(guān)于賽思

關(guān)于賽思