新華社最新消息,我國率先搭建了國際首個通信與智能融合的6G外場試驗網(wǎng),實現(xiàn)了6G主要場景下通信性能的全面提升。基于6G場景對時鐘信號的高要求,賽思設(shè)計了一種開環(huán)結(jié)構(gòu)的小數(shù)分頻鎖相環(huán)量化噪聲校準(zhǔn)技術(shù),并自研了高性能SOC時鐘芯片產(chǎn)品。

相較于5G,6G不僅能夠達(dá)到更高速率、更低時延、更廣的連接密度,還能實現(xiàn)通信與人工智能、智能感知的深度融合。這也意味著“快”只是6G通信技術(shù)中的一個基礎(chǔ)體現(xiàn),協(xié)同感知的智能管理才是其顛覆性的創(chuàng)新點。

從5G到6G,通信基站從僅支持通信信號的發(fā)送和接受升級至同時支持通信和感知,這便要求應(yīng)用于通信系統(tǒng)的片上系統(tǒng)SOC擁有多種不同頻率、不同性能的時鐘信號,以支持復(fù)雜的信號處理、高速數(shù)據(jù)處理、高質(zhì)量通信和智能感知管理需求。同時,還需最大限度地降低時鐘抖動可能對誤碼率、通信鏈路的穩(wěn)定可靠性等產(chǎn)生的影響。

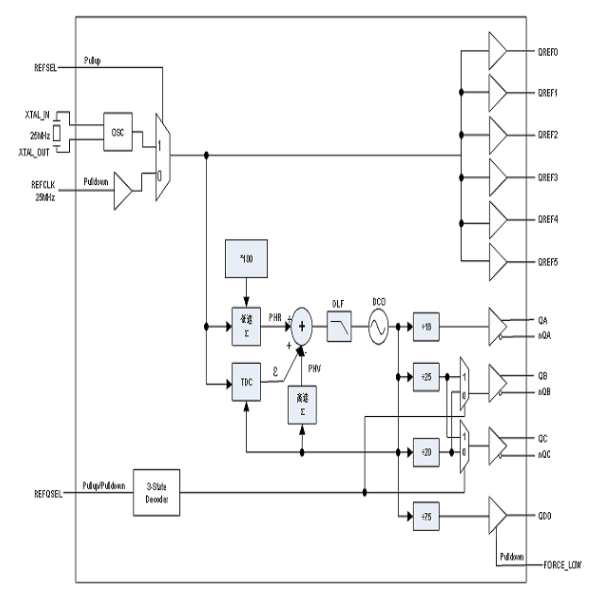

傳統(tǒng)的SOC模擬鎖相環(huán)面積大且僅有一路輸出信號,盡管數(shù)字型小數(shù)鎖相環(huán)可以克服面積、功耗等問題,但是時間數(shù)字轉(zhuǎn)換器Time-to-Digital Converter(TDC)、分?jǐn)?shù)分頻器量化噪聲、數(shù)字控制振蕩器Digital Controlled Oscillator(DCO)的相位噪聲之間的折中無法避免,且極大地影響著輸出的時鐘抖動。

因此如何在SOC上提供多個鎖相環(huán)時鐘信號,同時降低面積、功耗和時鐘抖動成業(yè)界關(guān)切的重點。基于此,賽思設(shè)計了一種開環(huán)結(jié)構(gòu)的小數(shù)分頻鎖相環(huán)量化噪聲校準(zhǔn)技術(shù),并研制了可應(yīng)用于6G通信技術(shù)的高性能SOC時鐘芯片。

一種開環(huán)結(jié)構(gòu)的小數(shù)分頻鎖相環(huán)量化噪聲校準(zhǔn)技術(shù)

一種開環(huán)結(jié)構(gòu)的小數(shù)分頻鎖相環(huán)量化噪聲校準(zhǔn)技術(shù)是為了滿足5G/6G高速數(shù)據(jù)通信系統(tǒng)中,片上系統(tǒng)SOC對時鐘信號的高要求而設(shè)計的。

該設(shè)計的的四大亮點:

1、消除量化噪聲,降低時鐘抖動。在互補DTC校準(zhǔn)技術(shù)的基礎(chǔ)上,提出了量化噪聲校準(zhǔn)技術(shù),消除量化噪聲,同時可以進一步提高FOD時鐘輸出的整體噪聲性能;

2、降低面積、功耗。本技術(shù)減少了DTC在數(shù)字控制字為0時候的補償電路,減少了DTC數(shù)量,進而降低功耗和面積;

3、避免了頻率雜散抽取、鎖相環(huán)濾波等校準(zhǔn)技術(shù)帶來的電路復(fù)雜度;

4、全后臺校準(zhǔn),相對原來的前臺校準(zhǔn)+后臺校準(zhǔn),提出的全后臺校準(zhǔn)技術(shù)對工藝電壓溫度Process Voltage Temperature(PVT)變化不敏感。

技術(shù)詳解:

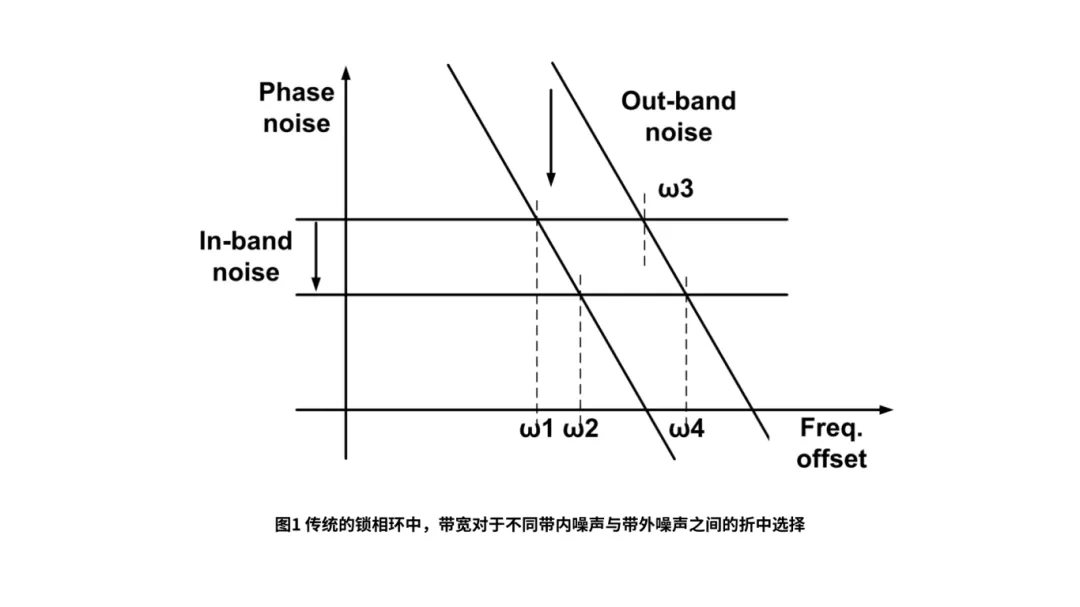

為了提升系統(tǒng)相位噪聲性能,在壓低帶外噪聲的情況下,本技術(shù)提出采用小帶寬的設(shè)計,壓縮帶內(nèi)噪聲對系統(tǒng)的貢獻,例如圖1中帶寬從w3-->w1。在振蕩器為主的帶外噪聲一定且比較高的情況下,為了提升相位噪聲性能,應(yīng)該在壓低帶內(nèi)噪聲的情況下,采用寬帶寬的設(shè)計,降低帶外噪聲對系統(tǒng)相位噪聲的貢獻,例如圖1中帶寬從w2-->w4。

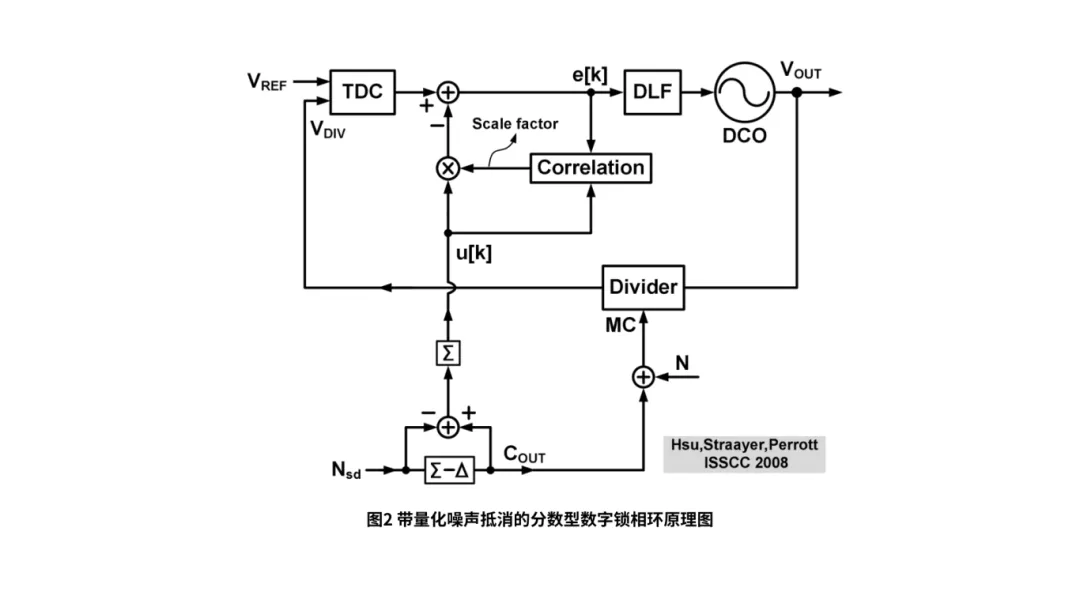

在閉環(huán)量化噪聲抵消的分?jǐn)?shù)型數(shù)字鎖相環(huán)中,通過將TDC的輸出e[k]與DSM的輸出u[k]進行相關(guān)處理產(chǎn)生比例因子,然后u[k]與比例因子相乘后的結(jié)果反饋并且與TDC輸出做差產(chǎn)生新的e[k],這樣消除量化噪聲,從而可以提高帶內(nèi)噪聲性能,進而采用大帶寬設(shè)計,得到優(yōu)異的系統(tǒng)噪聲性能。

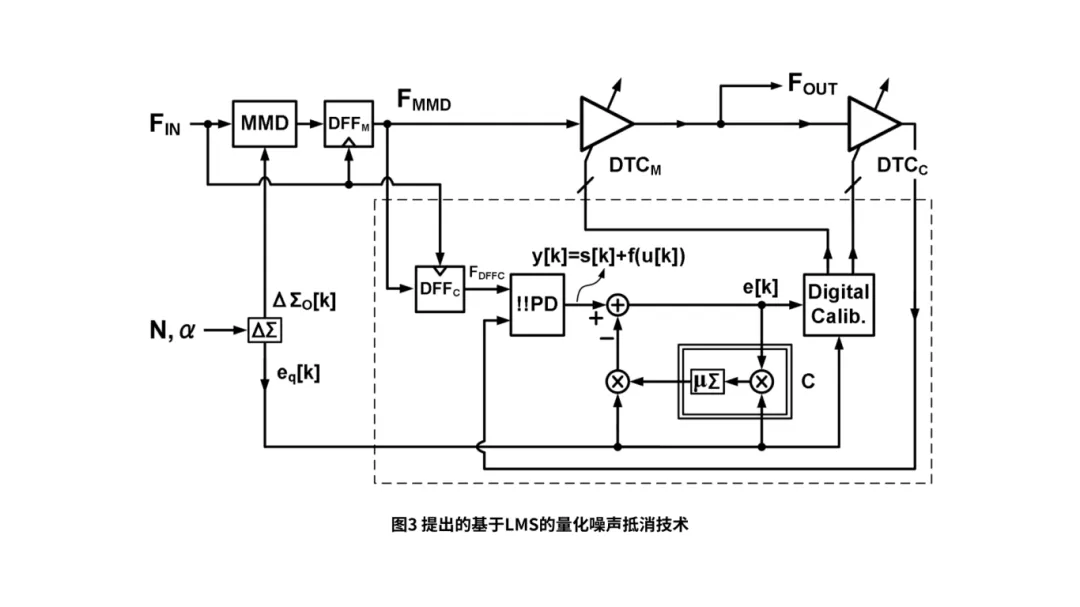

本技術(shù)通過將Bang-Bang Phase Detector(BBPD)的輸出e[k]與DSM的輸出eq[k]進行相關(guān)處理產(chǎn)生比例因子,然后eq[k]與比例因子相乘后的結(jié)果反饋并且與BBPD輸出做差產(chǎn)生新的e[k]。

賽思作為國內(nèi)首家為5G通信提供時頻同步解決方案的國家專精特新“小巨人”企業(yè),也是國內(nèi)三大移動通信運營商中國移動、中國電信、中國聯(lián)通5G同步網(wǎng)設(shè)備的核心供應(yīng)商,基于5G規(guī)模商業(yè)化及6G預(yù)研實踐需要,研制了高性能SOC時鐘芯片。

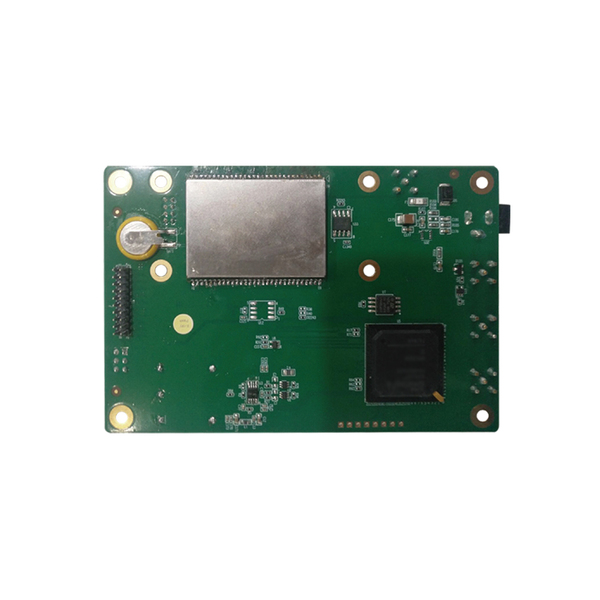

賽思高性能SOC時鐘芯片

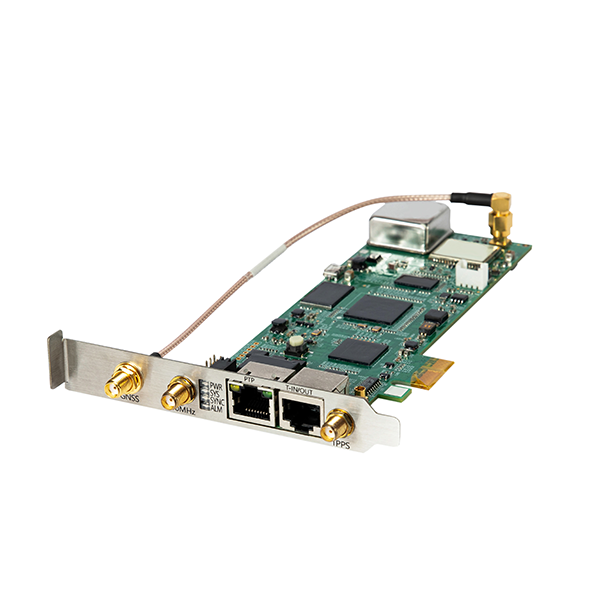

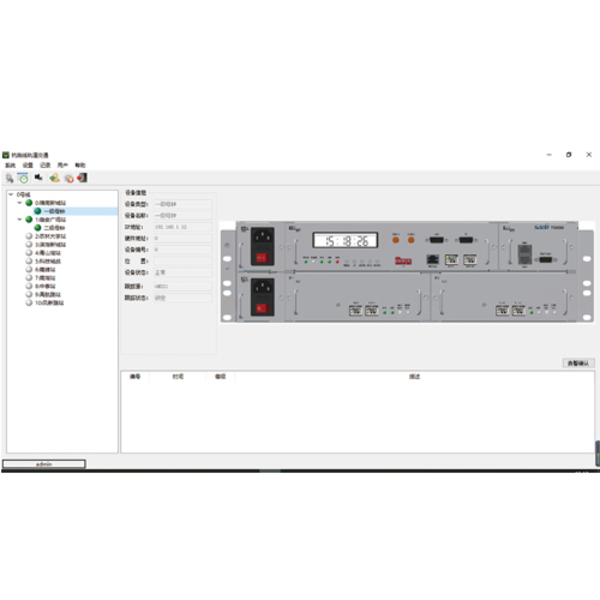

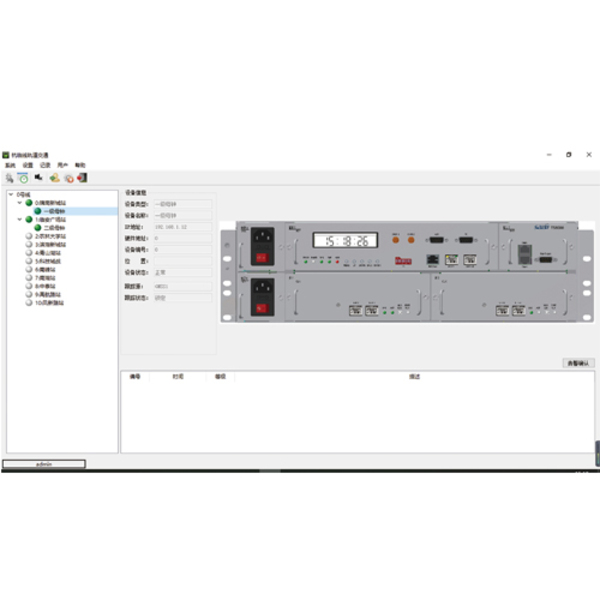

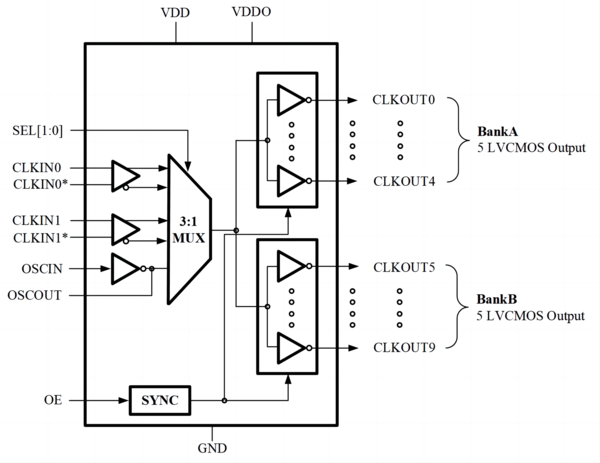

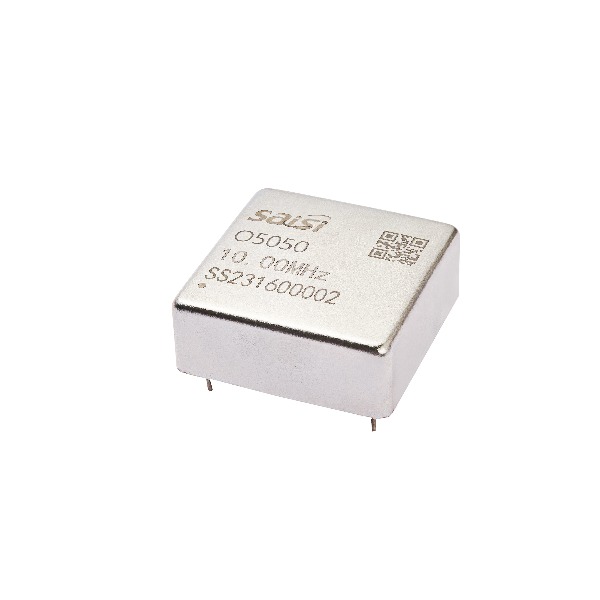

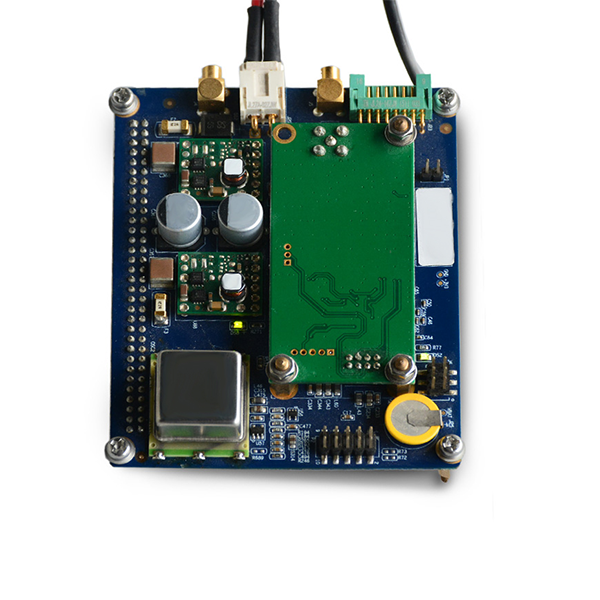

賽思高性能SOC時鐘芯片是基于自研的全數(shù)字鎖相環(huán) ADPLL 技術(shù),攻克了時間頻率處理功能微型化、時鐘抖動抑制、高精度時間誤差檢測等重難點問題,突破了全數(shù)字鎖相環(huán)、時間誤差檢測、時鐘同步算法、高頻時鐘分頻和驅(qū)動等關(guān)鍵技術(shù)瓶頸,將整個時鐘同步板卡的性能集成于一身,最終以SOC芯片的形態(tài)運用于時鐘授時、時頻傳輸鏈路和用時設(shè)備中,芯片體積較傳統(tǒng)時鐘時間同步處理模塊減小90%。

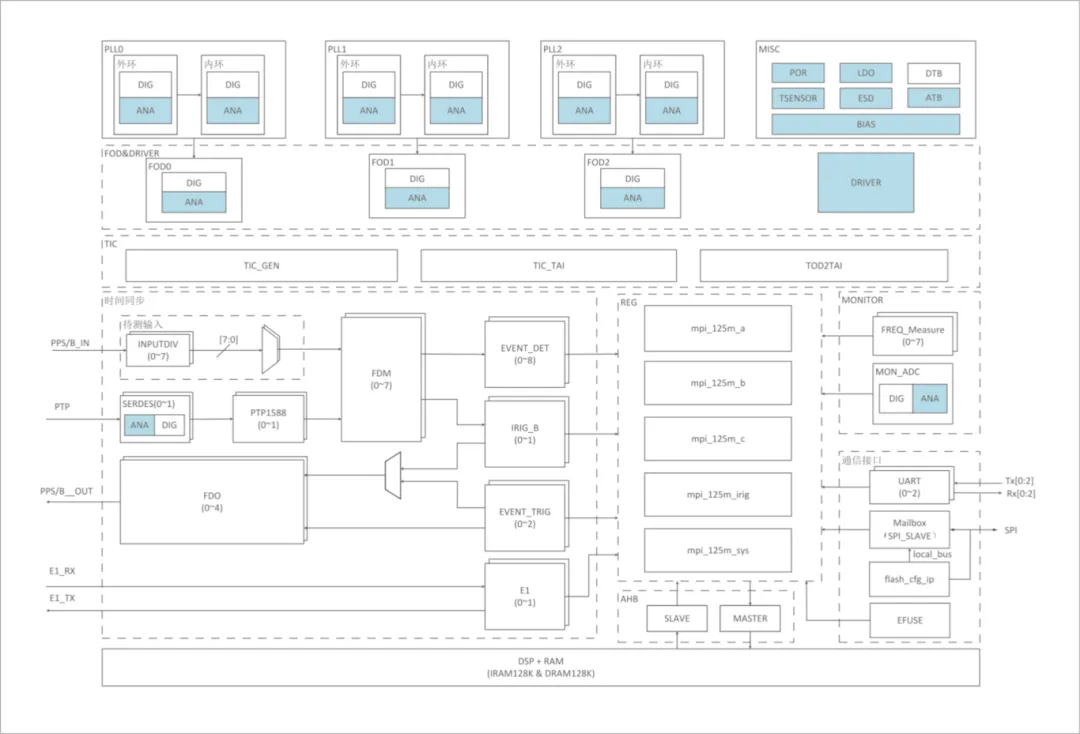

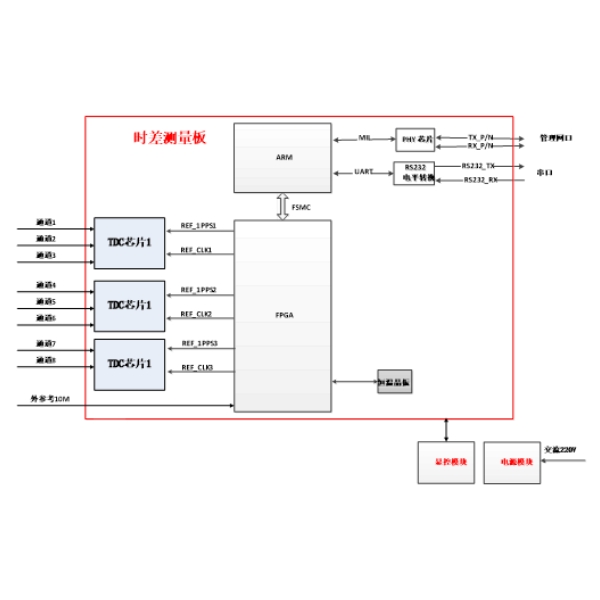

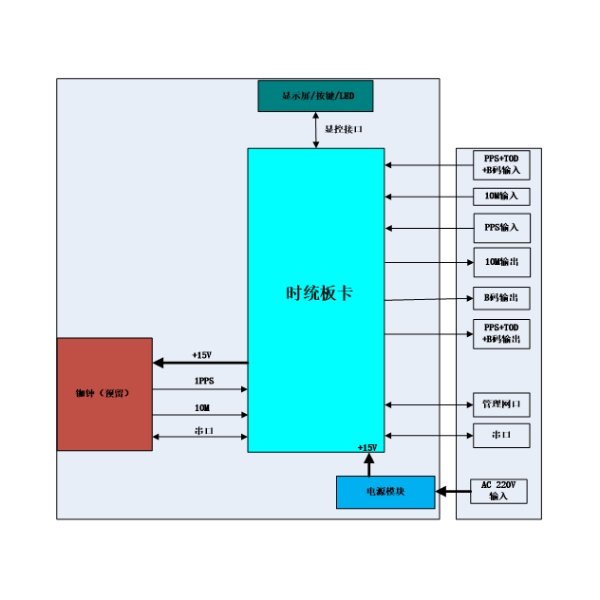

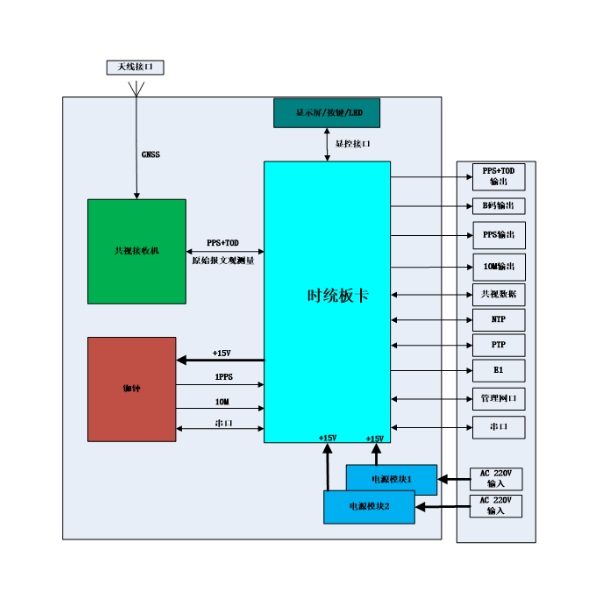

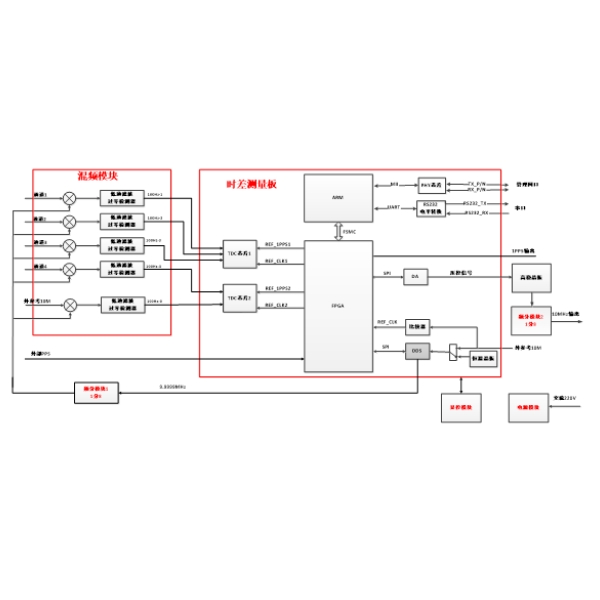

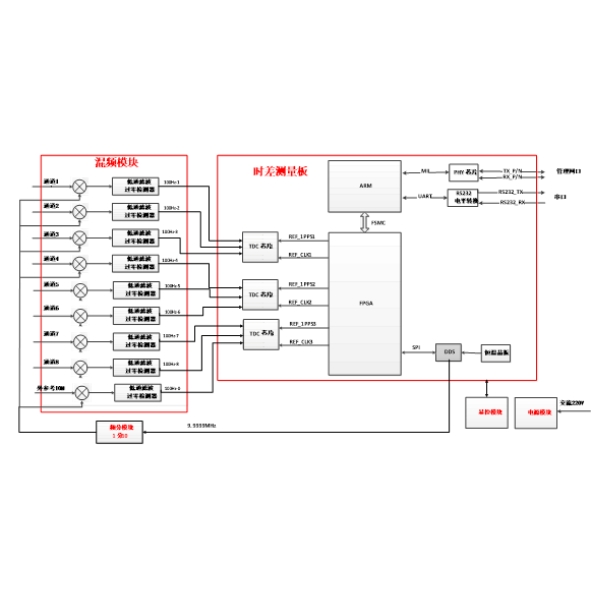

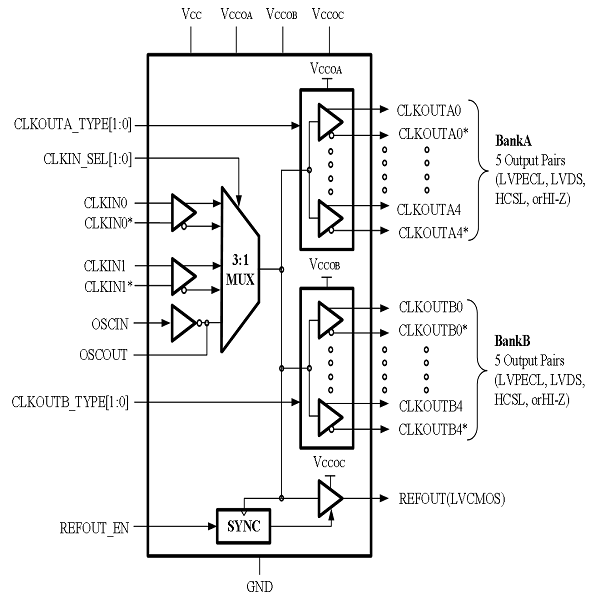

SOC時鐘芯片功能框架圖

同時產(chǎn)品具備時鐘輸出抖動優(yōu)于200飛秒的輸出特性(國際競品250飛秒),屬全球首創(chuàng),并于2023年當(dāng)選央視專精特新·制造強國「年度絕活」案例,目前已在5G/6G移動通信、軌道交通、金融證券等有高精度時頻同步需求的場景得到廣泛應(yīng)用。

賽思當(dāng)選央視專精特新·制造強國「年度絕活」案例步履不停,進步不止。作為時頻領(lǐng)域的標(biāo)桿,未來,賽思將繼續(xù)在時頻細(xì)分領(lǐng)域攻堅克難,用技術(shù)創(chuàng)新升級讓時頻技術(shù)始終走在前沿,不斷夯實自身科技硬實力,助力我國6G愿景實現(xiàn)。

時鐘系統(tǒng)

時鐘系統(tǒng)  芯片

芯片  晶振&原子鐘

晶振&原子鐘  授時板卡 NTP時間同步服務(wù)器PTP時間同步服務(wù)器時間同步裝置授時安全防護裝置網(wǎng)同步設(shè)備/時頻一體化設(shè)備子母鐘系統(tǒng)BBU池時間同步時統(tǒng)設(shè)備鐘組設(shè)備測試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時鐘發(fā)生器時鐘緩沖器時鐘SOC芯片超低噪聲OCXO超高穩(wěn)OCXO小型化OCXO溫補晶振TCXO原子鐘時鐘模塊授時模塊

授時板卡 NTP時間同步服務(wù)器PTP時間同步服務(wù)器時間同步裝置授時安全防護裝置網(wǎng)同步設(shè)備/時頻一體化設(shè)備子母鐘系統(tǒng)BBU池時間同步時統(tǒng)設(shè)備鐘組設(shè)備測試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時鐘發(fā)生器時鐘緩沖器時鐘SOC芯片超低噪聲OCXO超高穩(wěn)OCXO小型化OCXO溫補晶振TCXO原子鐘時鐘模塊授時模塊

智能電網(wǎng)

智能電網(wǎng)

通信網(wǎng)絡(luò)

通信網(wǎng)絡(luò)

智慧交通

智慧交通

智能樓宇

智能樓宇

數(shù)據(jù)中心

數(shù)據(jù)中心

前沿領(lǐng)域

前沿領(lǐng)域

新聞資訊

新聞資訊

聯(lián)系我們

聯(lián)系我們

人才研學(xué)中心

人才研學(xué)中心

加入賽思

加入賽思

關(guān)于賽思

關(guān)于賽思