“時(shí)鐘信號(hào)是電子系統(tǒng)的脈搏,而時(shí)鐘緩沖器則是維持其穩(wěn)定跳動(dòng)的關(guān)鍵元件。”在高速數(shù)字電路設(shè)計(jì)中,時(shí)鐘信號(hào)的完整性直接影響著系統(tǒng)性能。隨著處理器主頻突破GHz級(jí)、多核架構(gòu)普及以及物聯(lián)網(wǎng)設(shè)備對(duì)低功耗需求的激增,時(shí)鐘緩沖器已從輔助元件演變?yōu)橄到y(tǒng)級(jí)設(shè)計(jì)的重要支撐。本文將深入剖析時(shí)鐘緩沖器在五大領(lǐng)域的創(chuàng)新應(yīng)用,揭示其如何通過信號(hào)整形、相位同步、功耗優(yōu)化等技術(shù)手段,推動(dòng)現(xiàn)代電子系統(tǒng)突破性能瓶頸。

一、高速數(shù)字系統(tǒng)的時(shí)鐘樹優(yōu)化

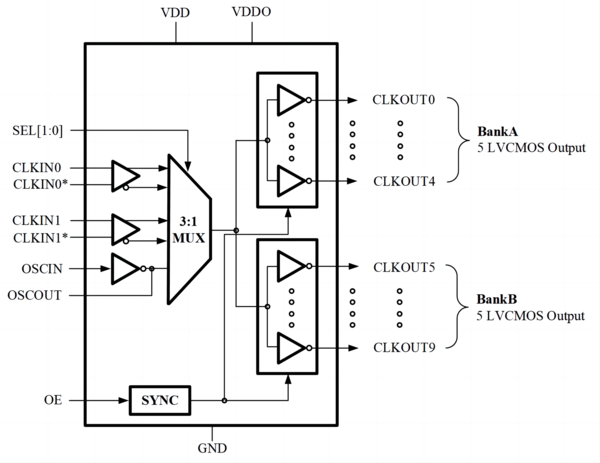

在FPGA、GPU等超大規(guī)模集成電路中,時(shí)鐘信號(hào)需要驅(qū)動(dòng)數(shù)百個(gè)終端負(fù)載。傳統(tǒng)直接驅(qū)動(dòng)方式會(huì)導(dǎo)致時(shí)鐘偏移(Clock Skew)累積,造成時(shí)序錯(cuò)亂。

時(shí)鐘扇出擴(kuò)展:通過級(jí)聯(lián)低阻抗輸出緩沖器,將單一時(shí)鐘源擴(kuò)展至128路同相信號(hào)

阻抗匹配補(bǔ)償:內(nèi)置可編程終端電阻(50Ω/75Ω/100Ω)消除傳輸線反射

動(dòng)態(tài)延遲調(diào)節(jié):集成數(shù)控延遲線(步進(jìn)精度10ps)修正布線差異

二、多處理器架構(gòu)的時(shí)鐘域管理

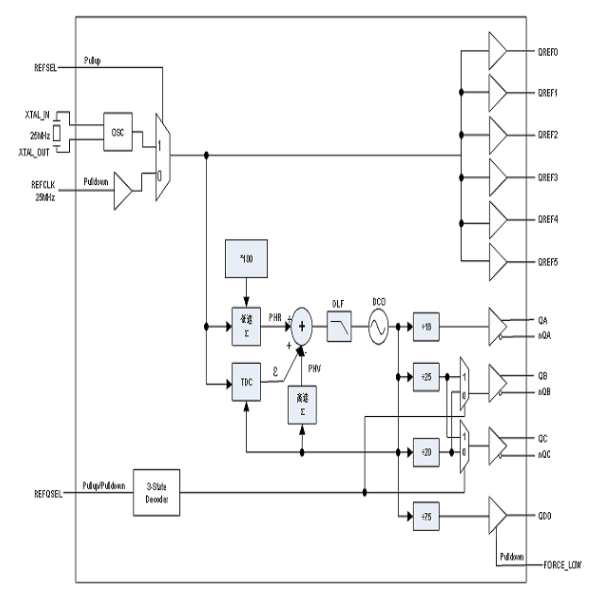

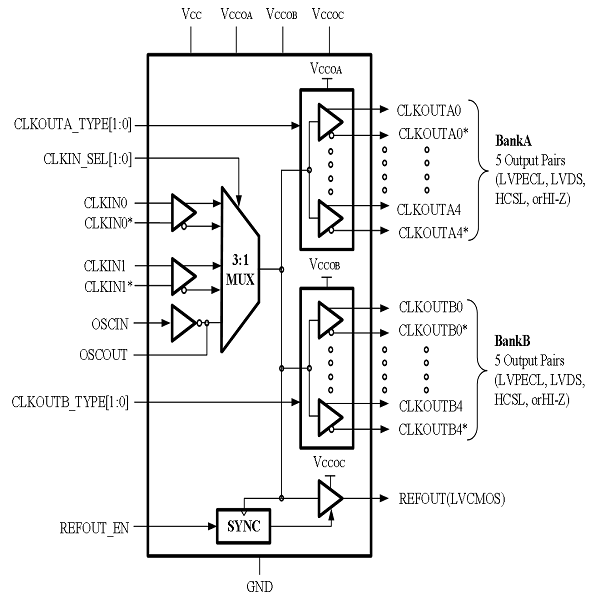

異構(gòu)計(jì)算平臺(tái)常包含ARM核、DSP模塊和硬件加速器,各單元工作頻率差異可達(dá)5倍以上。差分時(shí)鐘緩沖器通過以下技術(shù)實(shí)現(xiàn)跨時(shí)鐘域協(xié)同:

1. 多頻點(diǎn)生成:基于PLL的倍頻/分頻電路,從100MHz基準(zhǔn)生成1.2GHz/800MHz/200MHz三組時(shí)鐘

2. 相位對(duì)齊:內(nèi)置鑒相器自動(dòng)校準(zhǔn)DDR4內(nèi)存控制器與CPU的時(shí)鐘邊沿

3. 抖動(dòng)過濾:采用LC諧振腔濾除開關(guān)電源引入的10-100MHz帶內(nèi)噪聲

三、高速通信接口的信號(hào)完整性保障

PCIe 5.0、400G以太網(wǎng)等接口的速率突破32Gbps后,時(shí)鐘質(zhì)量成為鏈路穩(wěn)定的生命線。時(shí)鐘緩沖器在光模塊中的應(yīng)用證明:

預(yù)加重處理:通過可調(diào)預(yù)加重電路(0-6dB)補(bǔ)償FR4板材的高頻衰減

共模噪聲抑制:差分架構(gòu)將CMRR指標(biāo)提升至45dB@10GHz

四、可編程邏輯器件的動(dòng)態(tài)重構(gòu)支持

FPGA的Partial Reconfiguration技術(shù)需要時(shí)鐘網(wǎng)絡(luò)動(dòng)態(tài)切換。時(shí)鐘緩沖器通過以下創(chuàng)新滿足需求:

熱插拔時(shí)鐘切換:采用無縫切換技術(shù)(Glitch-Free Switching),切換時(shí)間<1ns

多區(qū)域供電:支持1.0V/1.2V/1.8V混合電壓域驅(qū)動(dòng)

動(dòng)態(tài)功耗調(diào)節(jié):根據(jù)負(fù)載數(shù)量自動(dòng)調(diào)整驅(qū)動(dòng)強(qiáng)度,靜態(tài)功耗降低67%

五、物聯(lián)網(wǎng)設(shè)備的低功耗時(shí)鐘架構(gòu)

針對(duì)NB-IoT等電池供電設(shè)備,時(shí)鐘緩沖器突破傳統(tǒng)方案局限:

納米級(jí)功耗管理:深度休眠模式電流僅850nA,喚醒時(shí)間<2μs

溫度補(bǔ)償算法:在-40℃~85℃范圍內(nèi)保持±5ppm頻率穩(wěn)定度

從上述應(yīng)用可見,時(shí)鐘緩沖器已超越簡單的信號(hào)驅(qū)動(dòng)功能,正在向智能化、自適應(yīng)化方向演進(jìn)。隨著3D封裝、光互連等新技術(shù)普及,其設(shè)計(jì)理念將持續(xù)重構(gòu)電子系統(tǒng)的時(shí)鐘架構(gòu)范式。

時(shí)鐘系統(tǒng)

時(shí)鐘系統(tǒng)  芯片

芯片  晶振&原子鐘

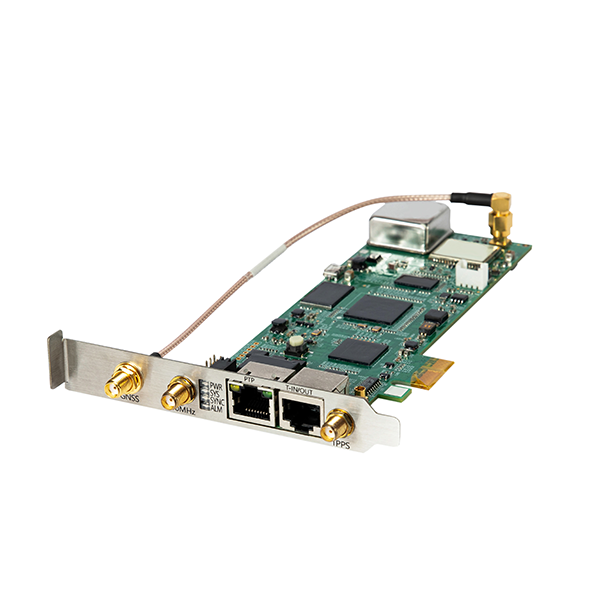

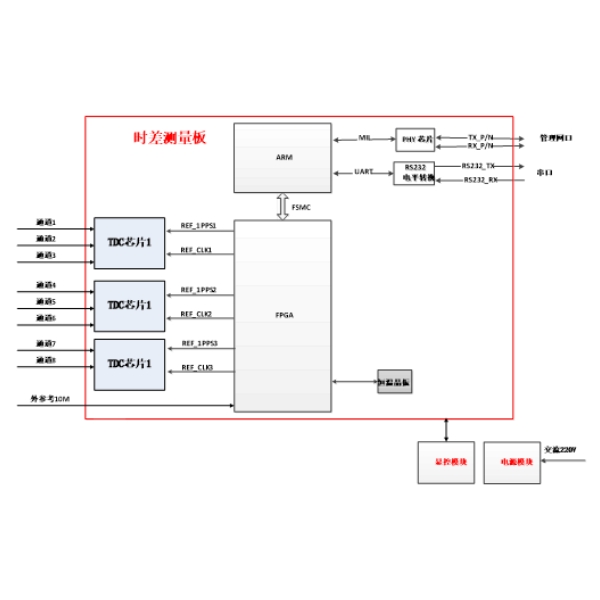

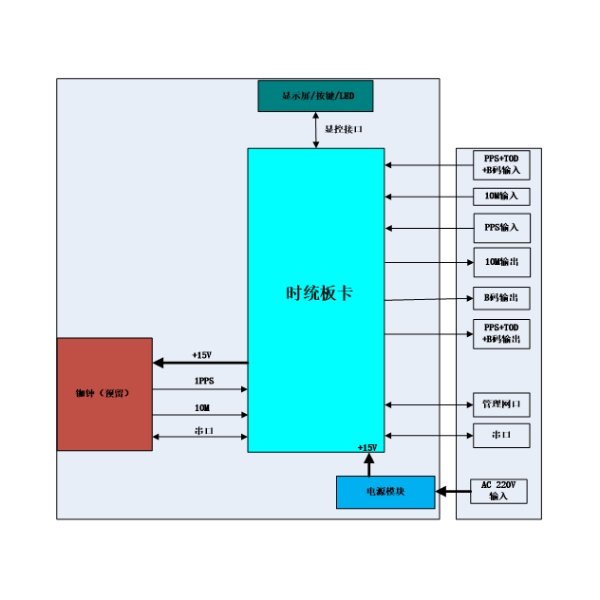

晶振&原子鐘  授時(shí)板卡 NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護(hù)裝置網(wǎng)同步設(shè)備/時(shí)頻一體化設(shè)備子母鐘系統(tǒng)BBU池時(shí)間同步時(shí)統(tǒng)設(shè)備鐘組設(shè)備測(cè)試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片超低噪聲OCXO超高穩(wěn)OCXO小型化OCXO溫補(bǔ)晶振TCXO原子鐘時(shí)鐘模塊授時(shí)模塊

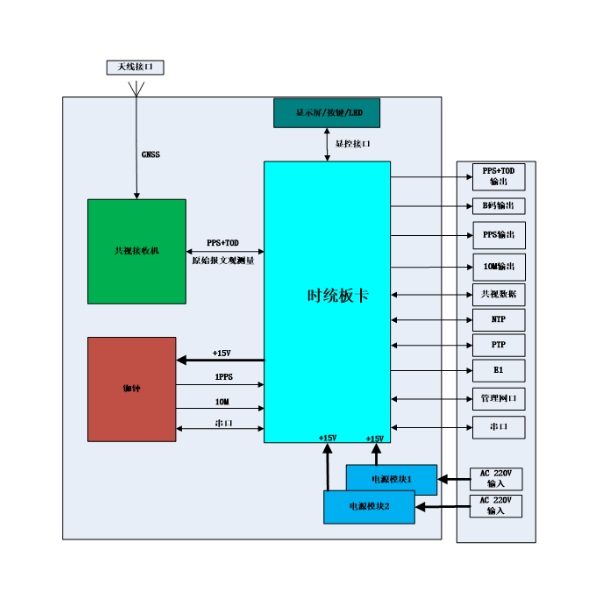

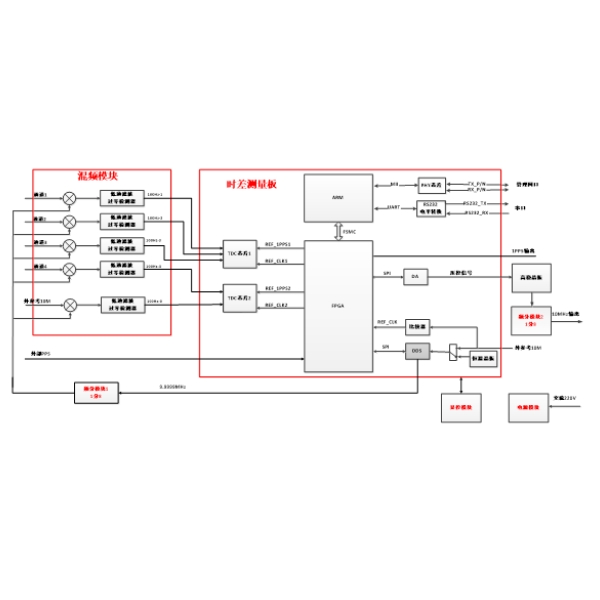

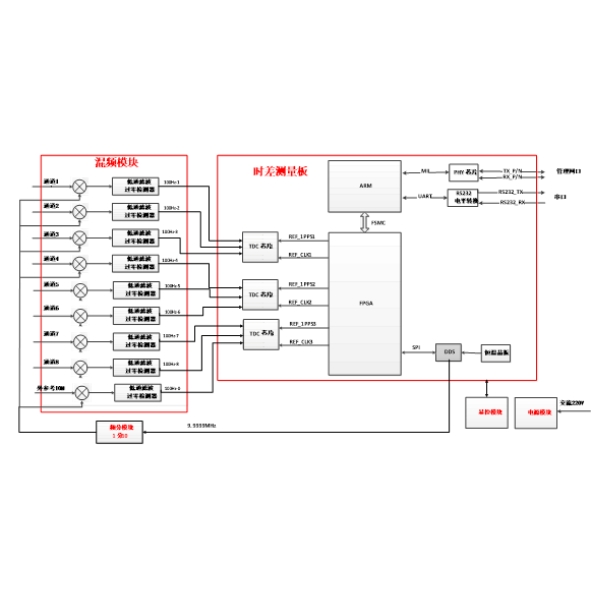

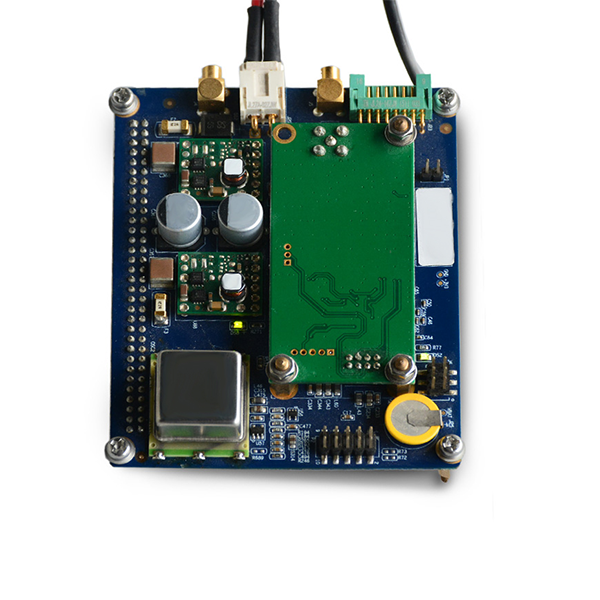

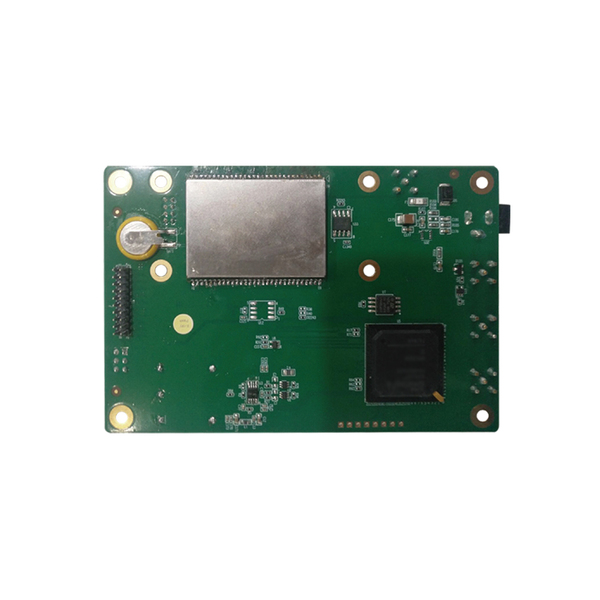

授時(shí)板卡 NTP時(shí)間同步服務(wù)器PTP時(shí)間同步服務(wù)器時(shí)間同步裝置授時(shí)安全防護(hù)裝置網(wǎng)同步設(shè)備/時(shí)頻一體化設(shè)備子母鐘系統(tǒng)BBU池時(shí)間同步時(shí)統(tǒng)設(shè)備鐘組設(shè)備測(cè)試儀器光纖雙向設(shè)備網(wǎng)管系統(tǒng)語音芯片時(shí)鐘發(fā)生器時(shí)鐘緩沖器時(shí)鐘SOC芯片超低噪聲OCXO超高穩(wěn)OCXO小型化OCXO溫補(bǔ)晶振TCXO原子鐘時(shí)鐘模塊授時(shí)模塊 子母鐘系統(tǒng)TS8000

子母鐘系統(tǒng)TS8000 電力時(shí)間同步裝置TS3000(4U)

電力時(shí)間同步裝置TS3000(4U) NTP時(shí)間服務(wù)器TS3000(1U)

NTP時(shí)間服務(wù)器TS3000(1U) 模塊化NTP服務(wù)器TS3000

模塊化NTP服務(wù)器TS3000 時(shí)頻同步設(shè)備/網(wǎng)同步設(shè)備SM2000

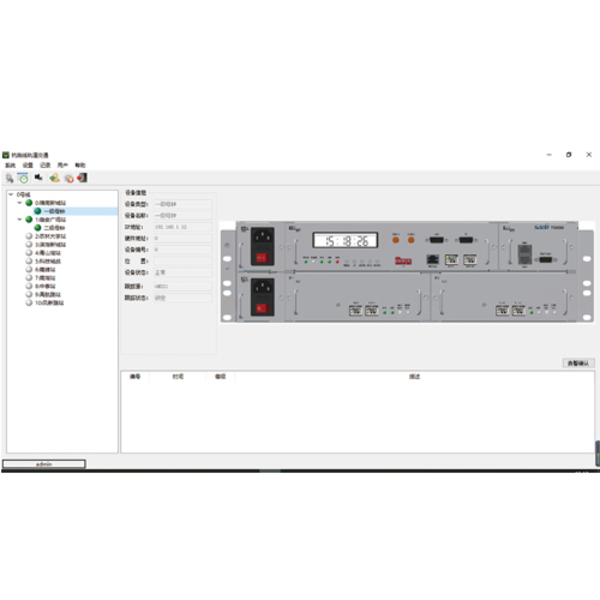

時(shí)頻同步設(shè)備/網(wǎng)同步設(shè)備SM2000 同步網(wǎng)綜合網(wǎng)管

同步網(wǎng)綜合網(wǎng)管 TS8000擴(kuò)展箱/NTP/RS422

TS8000擴(kuò)展箱/NTP/RS422 萬兆接口NTP服務(wù)器NS7200(2U)

萬兆接口NTP服務(wù)器NS7200(2U) 高性能NTP服務(wù)器NS7200

高性能NTP服務(wù)器NS7200 室外型PTP服務(wù)器LF7310

室外型PTP服務(wù)器LF7310 綜合時(shí)統(tǒng)設(shè)備LF7300

綜合時(shí)統(tǒng)設(shè)備LF7300 綜合時(shí)統(tǒng)設(shè)備LF7350

綜合時(shí)統(tǒng)設(shè)備LF7350 GPS/北斗智能分路系統(tǒng)GNSS100/200

GPS/北斗智能分路系統(tǒng)GNSS100/200

智能電網(wǎng)

智能電網(wǎng)

通信網(wǎng)絡(luò)

通信網(wǎng)絡(luò)

智慧交通

智慧交通

智能樓宇

智能樓宇

數(shù)據(jù)中心

數(shù)據(jù)中心

前沿領(lǐng)域

前沿領(lǐng)域

新聞資訊

新聞資訊

聯(lián)系我們

聯(lián)系我們

人才研學(xué)中心

人才研學(xué)中心

加入賽思

加入賽思

關(guān)于賽思

關(guān)于賽思